# Research Accelerator for Multiple Processors

## Architecture, Language & Compiler

### Introducing RAMP

- Research Accelerator for Multiple Processors.

Originally envisioned as a cross platform architectural simulator.

Designed to foster community research (Share & verify results).

- A distributed event simulation & message passing system framework.

Orders of magnitude faster than existing solutions.

Eases component re-use and integration.

- A modeling language (RDL) is a key step in the realization of RAMP.

The “Target System,” the system being emulated, is captured in RDL and emulated on the “Host System” (an FPGA or CPU)

### The “Counter” Example

```

unit {

input  bit[1]

output bit[32]           UpDown;

output bit[32]           Count;

output Counter;          Counter;

}

unit {

output bit[11]

attribute Calinx2;

attribute Calinx2;

}           Value;

"input:1:SW_";

"input:1:BTN_";

IO::BooleanInput;

platform {

language

default link

}

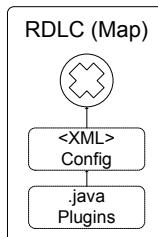

map {

platform Calinx2

unit     CounterExample

BasePlatformInst;

BaseUnitInst;

Calinx2Counter;

}

unit {

instance IO::BooleanInput

instance Counter

instance IO::Display7Seg

BooleanInput;           Counter;

Display7Seg;           Value;

BooleanInput;           Display7Seg;

}

channel fifopipe[1, 1, 1] InChannel

{ BooleanInput.Value -> Counter.UpDown };

channel fifopipe[32, 1, 1] OutChannel

{ Counter.Count -> Display7Seg.Value };

CounterExample;

}

```

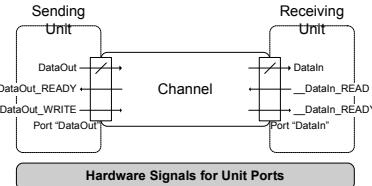

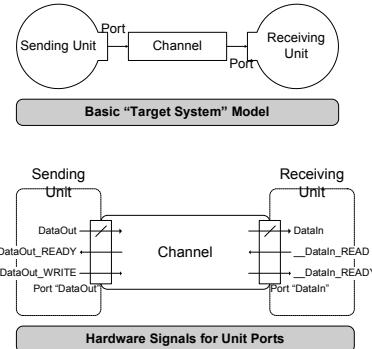

### The “Target System” Model

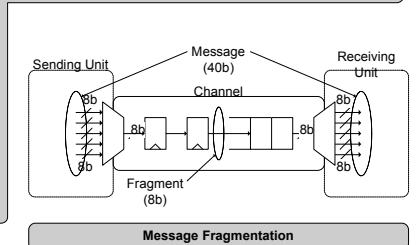

- Units communicate over point-to-point, unidirectional channels

A unit would be ~10,000 gates (Processor + L1 cache)

Units are implemented in the “host” language, eg. Verilog

Existing message passing hardware/software can be ported easily

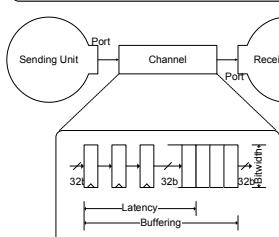

- Channels include a delay model

Allows timing simulations

Statically typed, variable size messages

Bitwidth (Fragment)

Latency

Buffering

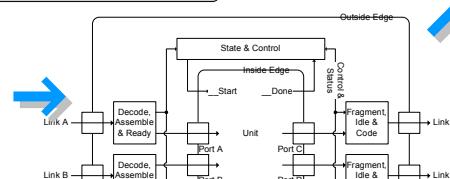

### RDL Compiler Toolflow

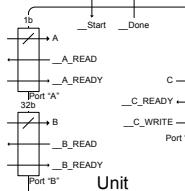

- A simple unit

Three ports

Unstructured messages

- No functionality in RDL

```

unit {

input  bit[1]

input  bit[32]     A;

output bit[12]    B;

output Unit;

}

```

- Unit shell, ready for implementation

- Verilog, Java, etc...

- RDL Hierarchical Netlist

- Include channel model

- Flexible, extensible back end

- Support for multiple target languages

- Automatic cross platform implementation

- Complete host implementation